2.2.1

Summary Description

NEXSYS Defined Logic components consist of four configuration types of a Series C (8 Pin) component. The two input/four output interface (Figure 2.2.1.0-A) is designed to function as a digital electronic circuit controller that can perform Boolean logic gate operations AND, OR, NOT, NAND, NOR, XOR, XNOR, as well as BUFFER. The robust internal circuitry performs exceptionally well for use in wave and pulse shaping applications, as is typical in high-noise environments. Additional Defined Logic applications include Binary (BNR) and Binary-Coded Decimal (BCD) encoding for use in computing and other digital electronic circuit applications.

The NEXSYS Defined Logic (DL1, DL2, DL3, DL4) is a commercial-off-the-shelf (COTS) item. This standard catalog hardware includes features to allow for flexible interface design solutions while also meeting aircraft performance standards. The DL is designed, tested, and qualified to MIL-PRF-22885/116, MIL-PRF-22885/117, DO-160 and MIL-STD-461 requirements. Specifications are available in our MIL-PRF and DO-160 Documents page, and the qualification table is available in Appendix A.

There are four configuration types:

- Defined Logic 1 (DL1) is a combinational logic gate device that performs an Exclusive-OR (XOR) and Exclusive-NOR (XNOR) by decoding two (tied) pairs of four logic inputs to control two orthogonal outputs.

- Defined Logic 2 (DL2) decodes two independent Boolean logic gates (Channel 1 and 2). Each gate has two inputs that control one dedicated output.

- Defined Logic 3 (DL3) is a combinational Boolean logic gate device that decodes two independent logic gates, which cascade to a third gate to control two orthogonal outputs.

- Defined Logic 4 (DL4) is a combinational Boolean logic gate device that decodes four inputs to control two orthogonal outputs.

Input Characteristics

NEXSYS Defined Logic inputs are Power (28V), Ground (GND) and Logic Inputs (A, B, C, D). Defined Logic input circuity is diode isolated, buffered, and debounced for reliable operation. See additional sections for specific details concerning the Input/Output (I/O) interface. The inputs include the following characteristics for custom Boolean logic circuit control.

28V (PIN 4): Operating Voltage (Nom.), 4 mA Current Draw (Max.).

GND (PIN 5): Continuous Ground required, otherwise, inadvertent operation could occur.

A (PIN 1), B (PIN 2), C (PIN 3), D (PIN 7): Digital electronic inputs that detect logic level signals (1 or 0).

Input Options and Characteristics

NEXSYS Defined Logic inputs will detect signal levels that are present upon power-up. The input options involve specifying Pins A and C as either Pull-up or Pull-down to define the detected logic levels. Default levels are detected as either Logic High (1) or Logic Low (0) when the input signal is not active. For the DL1 variant only, inputs A and C are specified identically (Pull-up or Pull-down) since they are wired together externally. Inputs B and D are factory-configured and fixed as Pull-up.

The following describes the logic level detection options of inputs A and C and the fixed logic level detection definitions of inputs B and D. Configuring a Defined Logic part number to meet specific application requirements is accomplished by utilizing the online Part Configurator.

Inputs A and C, specified as Pull-up (U): The logic level is detected as Logic High (1) when above +4 VDC or High-Z (Open), and a Logic Low (0) when below +1.2 VDC.

Inputs A and C, specified as Pull-down (D): The logic level is detected as Logic High (1) when above +4 VDC, and a Logic Low (0) when below +1.2 VDC or High-Z (Open).

Inputs B and D, fixed as Pull-up (U): The signal level is detected as Logic High (1) when it is above +4 VDC or High-Z (Open), and a Logic Low (0) when below +1.2 VDC.

Note: If the input signal level transitions between +28 VDC and Low (Ground), either Pull-up or Pull-down may be specified since the High-Z (Open) level does not occur. If an input remains unused, the detected signal level (0 or 1) is defined by its Pull-up or Pull-down configuration.

Output Characteristics

NEXSYS Defined Logic active output signal levels are designated as 1 or 0, similar to input logic levels. However, output level definitions differ from the inputs, which are also designated as either 1 or 0. The following defines the Active Output signal levels.

Active High-Z (Open), (1) Output: The output signal level is defined as High-Z (Open).

Active Low (Ground), (0) Output: The output signal level is defined as Ground.

Note: All outputs are open-drain High-Z (Open) when not active and, therefore, do not require external sneak path isolation circuitry. The output load capacity is 2.0 A, see Figure 2.2.1.5-A (Operating Parameters) for electrical load rating types.

2.2.1.1

The Defined Logic 1 (DL1) is a combinational logic gate device that decodes two (tied) pairs of four logic inputs to control two orthogonal outputs, see Figure 2.2.1.1-A.

Application Performance

The DL1 is a digital electronic logic circuit controller that performs the Exclusive-OR (XOR) and Exclusive-NOR (XNOR) logic gate operations. OUT Y is Active High (1) or High-Z (Open) when both pairs of inputs are identical, and Active Low (0) or Ground when one pair is Low (0), and the other pair is High (1), Z is the complement of Y.

Combinational Logic Gate Options

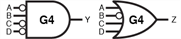

The DL1 combines logic gates to implement digital circuits that solve more complex functions. For example, the gate-level digital circuit diagram below demonstrates how the XOR and XNOR operations are performed, see Figure 2.2.1.1-B. The XOR and XNOR logic gate operations are dedicated functions integral to the DL1, and both are performed in a single component.

With Inputs, AC externally wired together and BD externally wired, OUT Z performs the XOR=TRUE expression if AC OR BD is High (1), but not both. Conversely, with Inputs, AC externally wired together and BD externally wired, OUT Y performs the XNOR=TRUE expression if AC OR BD is High (1), but not both. Figure 2.2.1.1-C, Figure 2.2.1.1-D, and Figure 2.2.1.1-E define the XOR and XNOR=TRUE expressions and logic statements.

|

XOR Gate Symbol |

Expression: XOR=TRUE |

||

|

|

The Exclusive-OR (XOR) gate produces an Active Open (1) output if either, but not both, of its inputs is High (1). |

||

|

Equation |

Variation |

TRUTH TABLE |

Boolean Logic “if” Statement |

|

|

|

|

if AC is High (1) OR BD is High (1), then Z is Open (1) else Z is Ground (0), Y is the complement of Z. |

|

XNOR Gate Symbol |

Expression: XNOR=TRUE |

||

|

|

The Exclusive-NOR (XNOR) gate produces an Active Ground (0) output if either, but not both, of its inputs is High (1). |

||

|

Equation |

Variation |

TRUTH TABLE |

Boolean Logic “if” Statement |

|

|

|

|

if AC is High (1) OR BD is High (1), Y is Ground (0) else Y is Open (1), Z is the complement of Y. |

| Inputs | Outputs: 1 = High-Z (Open), 0 = Low (Ground) | ||

| XOR | XNOR | ||

| A , C | B , D |

|

|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

2.2.1.2

The Defined Logic 2 (DL2) decodes two independent Boolean logic gates (Channel 1 and 2). Each gate has two inputs that control one dedicated output, see Figure 2.2.1.2-A

Application Performance

The DL2 is a digital electronic logic circuit controller that performs up to ten Boolean logic gate operations. The device allows the design flexibility of an independent, dual-channel device while also affording the wiring efficiencies of common power for both channels. Channel 1 consists of inputs A and B, which control OUT Y. Channel 2 consists of inputs C and D, which control OUT Z. Logic gate decodes are defined in the following truth table, see Figure 2.2.1.2-B - Figure 2.2.1.2-G, and Figure 2.2.1.2-H.

Boolean Logic Gate Options

The DL2 interface can function as a two-channel digital electronic circuit controller to perform the Boolean logic gate operations AND, OR, NOT, NAND, NOR, XOR, XNOR, as well as BUFFER. Each device consists of four inputs (A, B, C, D) and two outputs (Y,Z). The following tables detail the two-input logic gate operation of the DL2. Each channel has four variations, except BUFFER, and NOT. While digital notations also exist for equation Z = CD (Channel 2) , only Y = AB and Y = A (Channel 1) are depicted for simplicity, see Figure 2.2.1.2-B - Figure 2.2.1.2-G. The complete truth table for each Boolean logic gate operation is calculated as selections are made with the Part Configurator. The Boolean logic gate variations identified below are assigned based on part configuration. Variation number four, AND (4) and NOR (4), result in a logic gate equivalency (4=4). Likewise, variations specified as number eight, NAND (8) and OR (8), result in a logic gate equivalency (8=8). The following DL2 Boolean logic gate operations are also used to specify the first selection of the DL3 combinational logic circuit, see Defined Logic 3 (DL3).

| AND Gate Symbol | Boolean Expression: AND=TRUE | ||

|

|

The AND gate produces an Active Open (1) output only if all inputs are High (1). |

||

|

Equation |

Variation |

TRUTH TABLE |

Boolean Logic “if” Statement for Variations |

|

Y = A • B |

|

|

if A is High (1) AND B is High (1), then Y is Open (1) else Y is Ground (0). |

|

Y = A • B |

|

|

if A is High (1) AND B is Low (0), then Y is Open (1) else Y is Ground (0). |

|

Y = A • B |

|

|

if A is Low (0) AND B is High (1), then Y is Open (1) else Y is Ground (0). |

|

Y = A • B |

|

|

if A is Low (0) AND B is Low (0), then Y is Open (1) else Y is Ground (0). |

|

Figure 2.2.1.2-C |

|||

|---|---|---|---|

|

NAND Gate Symbol |

Expression: NAND=TRUE |

||

|

|

The NOT-AND (NAND) gate is equal to an AND gate followed by a NOT gate. The NAND gate produces an Active Open (1) output if any of the inputs are Low (0). |

||

|

Equation |

Variation |

TRUTH TABLE |

Boolean Logic “if” Statement |

|

Y = A • B |

|

|

if A is High (1) AND B is High (1), then Y is Ground (0) else Y is Open (1). |

|

Figure 2.2.1.2-D |

|||

|---|---|---|---|

| OR Gate Symbol | Boolean Expression: OR=TRUE | ||

|

|

The OR gate produces an Active Open (1) output if one OR more of its inputs are High (1). |

||

|

Equation |

Variation |

TRUTH TABLE |

Boolean Logic “if” Statement for Variations |

|

Y = A + B |

|

|

if A is High (1) OR B is High (1), then Y is Open (1) else Y is Ground (0). |

|

Y = A + B |

|

|

if A is High (1) OR B is Low (0), then Y is Open (1) else Y is Ground (0). |

|

Y = A + B |

|

|

if A is Low (0) OR B is High (1), then Y is Open (1) else Y is Ground (0). |

|

Y = A + B |

|

|

if A is Low (0) OR B is Low (0), then Y is Open (1) else Y is Ground (0). |

|

Figure 2.2.1.2-E |

|||

|---|---|---|---|

|

NOR Gate Symbol |

Expression: NOR=TRUE |

||

|

|

The NOT-OR (NOR) gate is equal to an OR gate followed by a NOT gate. The NOR gate produces an Active Ground (0) output if any of the inputs are High (1). |

||

|

Equation |

Variation |

TRUTH TABLE |

Boolean Logic “if” Statement |

|

Y = A + B |

|

|

if A is High (1) OR B is High (1), then Y is Ground (0) else Y is Open (1). |

|

Figure 2.2.1.2-F |

|||

|---|---|---|---|

|

BUFFER Gate Symbol |

Expression: BUFFER=TRUE |

||

|

|

The BUFFER gate passes a filtered state of the input to its output. |

||

|

Equation |

Variation |

TRUTH TABLE |

Boolean Logic “if” Statement |

|

Y = A |

|

|

if A is High (1), then Y is Open (1); if A is Low (0), then Y is Ground (0). |

|

NOT Gate Symbol |

Expression: NOT=TRUE |

||

|

|

The NOT gate produces an inverted version of the input at its output. It is also known as an INVERTER. If the input variable is A, the inverted output is known as NOT A. |

||

|

Equation |

Variation |

TRUTH TABLE |

Boolean Logic “if” Statement |

|

Y = A |

|

|

if A is High (1), then Y is Ground (0); if A is Low (0), then Y is Open (1). |

|

2.2.1.3

The Defined Logic 3 (DL3) is a combinational logic gate device that decodes two independent logic gates, which cascade to a third gate to control two orthogonal outputs, see Figure 2.2.1.3-A.

Application Performance

The DL3 is a digital electronic logic circuit controller that performs cascaded Boolean logic gate operations. The device reduces the necessity of multiple components and wiring complexity by cascading three logic gate operations internal to the device. Logic Gate 1 (T) and Logic Gate 2 (S) operate as independent logic gates that are decoded and then cascaded into a third logic gate, which is decoded to control the two outputs (YZ). OUT Y (Logic Gate 3) is normally Active Low (0) or Ground until the decode of Logic Gate 1 (T) and Gate 2 (S) is TRUE, as determined by the specified configuration, Z is the complement of Y.

Combinational Logic Gate Options

The DL3 combines logic gates to reduce the number of gates (components) required for implementation in a logic circuit. The DL3 builds upon the functionality of the DL2. First, two independent Boolean logic gates are specified (Selection 1, see Figure 2.2.1.3-B.) using the same options offered for the DL2, see Figure 2.2.1.2-B - Figure 2.2.1.2-G. The results of the two Boolean logic gates (TS) are then cascaded into a third combinational gate (N1-N4) to represent the sum-of-products, to perform multiple logic gate operations. For example, two AND gates (AB, CD) can be interfaced to a combination logic gate (N1) to produce the results of the outputs (YZ), see Figure 2.2.1.3-B.

The gate-level digital circuit diagrams below (N1-N4) represent the combinational logic gate operations available with the DL3, see Figure 2.2.1.3-C - Figure 2.2.1.3-F and Figure 2.2.1.3-G. Each option (N1-N4) combines and decodes any variation of two Boolean logic gate operations, as defined in the DL2 section (Figure 2.2.1.2-B - Figure 2.2.1.2-G). Complete logic tables representing all combinational gate operations are calculated as selections are made with the Part Configurator. Both N1 combinational logic gate variations result in logic gate equivalences (N1=N1), as well as both N4 variations (N4=N4). The combinational logic gate variation N1 is the logical inverse of N4 ((N1)=N4), and N2 is the complement binary form (1’s complement) of the N3 variation.

| Expression: N1 = TRUE | |||

|---|---|---|---|

| Equation | Variation | TRUTH TABLE | Boolean Logic “if” Statement for Variations |

|

Y = T • S Z = T • S |

|

|

if T is High (1) AND S is High (1), then Y is Open (1) else Y is Ground (0), Z is the complement of Y. |

|

Y = T • S Z = T + S |

|

||

|

Figure 2.2.1.3-D |

|||

|---|---|---|---|

|

Expression: N2=TRUE |

|||

|

Equation |

N2 |

TRUTH TABLE |

Boolean Logic “if” Statement |

|

Y = T • S Z = T + S |

|

|

if T is High (1) AND S is Low (0), then Y is Open (1) else Y is Ground (0), Z is the complement of Y. |

|

Expression: N3=TRUE |

|||

|

Equation |

N3 |

TRUTH TABLE |

Boolean Logic “if” Statement |

|

Y = T • S Z = T + S |

|

|

if T is Low (0) AND S is High (1), then Y is Open (1) else Y is Ground (0), Z is the complement of Y. |

| Expression: N4=TRUE | |||

|

Equation |

Variation |

TRUTH TABLE |

Boolean Logic “if” Statement for Variations |

|

Y = T • S Z = T + S |

|

|

if T is Low (0) AND S is Low (0), then Y is Open (1) else Y is Ground (0), Z is the complement of Y. |

|

Y = T + S Z = T + S |

|

if T is High (1) OR S is High (1), then Y is Ground (0) else Y is Open (1), Z is the complement of Y. | |

|

2.2.1.4

The Defined Logic 4 (DL4) is a combinational logic gate device that decodes four inputs to control two orthogonal outputs, see Figure 2.2.1.4-A.

Application Performance

The Defined Logic 4 is a digital electronic logic circuit controller that performs Boolean logic gate operations based upon the decode of 4 inputs. The device can perform a 4-bit binary (BNR) or binary-coded decimal (BCD) decode. The device monitors the signal levels of four inputs and holds the state of the two orthogonal outputs until the inputs detect a state change. When the specified decode of Inputs ABCD = TRUE, OUT Y is active Open (1), and OUT Z is active Ground (0). Logic gate decodes are defined in the following truth table, see Figure 2.2.1.4-B.

Four-Input Logic Gate Options

NEXSYS Defined Logic components also offer the four-input (ABCD) AND operation, as well as OR such that one is the binary complement of the other, which produces the two orthogonal outputs (YZ). For example, the four-input (ABCD) AND gate operation produces an Active Open (1) OUT (Y) if all inputs are High (1) and the OR gate produces an Active Open (1) OUT (Z) if one OR more of its inputs are High (1). The four-input logic gates are dedicated functions integral to the DL4 component, and has 16 variations.

|

Four-Input Combination Gate Symbols |

Combinational Gate Expression |

||

|

|

The four input AND gate produces an Active Open (1) Y Output only if all inputs are High (1). The four input, combination OR gate (Z) is the complement of Y. |

||

|

Equation |

Variation |

TRUTH TABLE |

Boolean Logic “if” Statement |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if A AND B AND C AND D is High (1), then Y is Open (1), else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if A AND B AND C is High (1), when D is Low (0), then Y is Open (1), else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if A AND B AND D is High (1), when C is Low (0) then, Y is Open (1), else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if A AND B is High (1), when C AND D is Low (0), then Y is Open (1), else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if A AND C AND D is High (1), when B is Low (0) then, Y is Open (1), else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if A AND C is High (1), when B AND D is Low (0), then Y is Open (1), else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if A AND D is High (1), when B AND C is Low (0), then Y is Open (1), else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if A is High (1), when B AND C AND D is Low (0), then Y is Open (,1) else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if B AND C AND D is High (1), when A is Low (0) then, Y is Open (1), else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if B AND C High (1), when A AND D is Low (0), then Y is Open (1), else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if B AND D is High (1), when A AND C is Low (0), then Y is Open (1), else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if B is High (1), when A AND C AND D is Low (0), then Y is Open (,1) else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if C AND D is High (1), when A AND B is Low (0), then Y is Open (1), else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if C is High (1), when A AND B AND D is Low (0), then Y is Open (1,) else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if D is High (1), when A AND B AND C is Low (0), then Y is Open (1,) else Y is Ground (0), Z is the complement of Y. |

|

Y = A • B • C • D Z = A + B + C + D |

|

|

if A AND B AND C AND D is Low (0), then Y is Open (1), else Y is Ground (0), Z is the complement of Y. |

|

Figure 2.2.1.4-C |

|---|

|

2.2.1.5

| Description | Parameters |

| Operating Parameters | |

| Operating Voltage (Max. / Nom. / Min.) | +32 VDC / +28 VDC / +18 VDC |

| Power Supply Input Current | 4 mA (Maximum) |

| Reset From Power Loss at 25°C | 5 sec (Minimum) at +25° C |

| Hold Up On Power Loss at 25°C | 200 ms (Minimum) |

| Input Parameters | |

| Propagation Timing A, B, C & D to output at 25°C |

Low to High 20 ms (Maximum) |

| * High Level Input Voltage ( VIH ) at 25°C | +4 VDC (Minimum) |

| * Low Level Input Voltage ( VIL ) at 25°C | +1.2 VDC (Maximum) |

| Low Level Input Current ( IIL ) at 25°C | 1mA (Maximum) |

| All Pulled-up inputs are diode isolated | |

| Output Parameters | |

| Output Load Capacity | 2.0 A (Resistive) / 1.0 A (Motor) / 0.8 A (Inductive/Lamp) |

| On-State Resistance at 25°C | Typical 0.07 ohms / Maximum 0.09 ohms |

| Off-State Resistance at 25°C | Open Drain (High-Z), Fuse-Protected MOSFET, +32 VDC Maximum |

| Temperature | |

| Operating & Non-Operating | -55° C to +85° C |

| Reliability

MIL-HDBK-217F, Notice 2 |

|

| Airborne Inhabited Cargo (AIC)

at 40° C Continuous Operation |

MTBF = 131,574 hrs |

| * VIL and VIH specifications are in reference to unit Ground. | |

For Qualification Summary, see Appendix A