### PERFORMANCE SPECIFICATION SHEET

SWITCH, PUSHBUTTON, ACCESSORY, OPTIONAL ELECTRONIC COMPONENT (OEC), SWITCHING AND LOGIC FUNCTION, LOW LEVEL, STAND-ALONE THROUGH HOLE-SOLDERABLE, AND COMMON TERMINATION SYSTEM (CTS) COMPATIBLE WITH MIL-PRF-22885/108 AND MIL-PRF-22885/113 PUSHBUTTON SWITCHES AND MIL-PRF-22885/116 MODULE

This specification is approved for use by all Departments and Agencies of the Department of Defense.

The complete requirements for acquiring the switches described herein shall consist of this specification and the latest issue of MIL-PRF-22885.

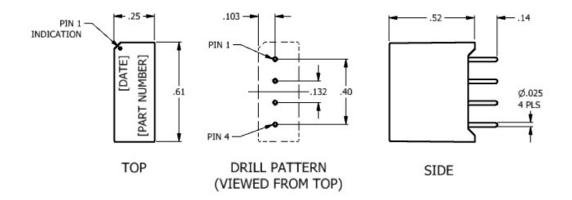

NOTES:

- 1) Unless otherwise noted, all dimensions are in inches. The tolerance is +/- 0.005 for three decimals and +/- 0.010 for two decimals.

- 2) Component Dimensions shown in this figure are for solderable OECs only.

- 3) For OECs installed in enclosures defined by MIL-PRF-22885/108, /113 and /116, dimensions, pin size, pin nomenclature, pin spacing, and component size is determined by enclosure type and the compatibility to the corresponding Common Termination System (CTS).

FIGURE 1. Series A OEC, Solderable.

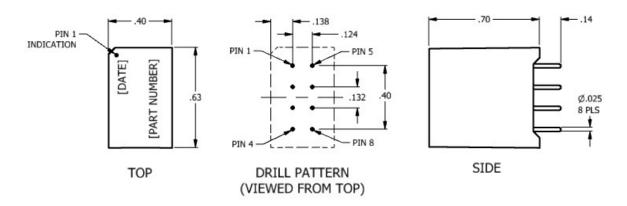

NOTES:

- 1) Unless otherwise noted, all dimensions are in inches. The tolerance is +/- 0.005 for three decimals and +/- 0.010 for two decimals.

- 2) Component Dimensions shown in this figure are for solderable OECs only.

- 3) For OECs installed in enclosures defined by MIL-PRF-22885/108, /113 and /116, dimensions, pin size, pin nomenclature, pin spacing, and component size is determined by enclosure type and the compatibility to the corresponding Common Termination System (CTS).

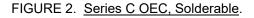

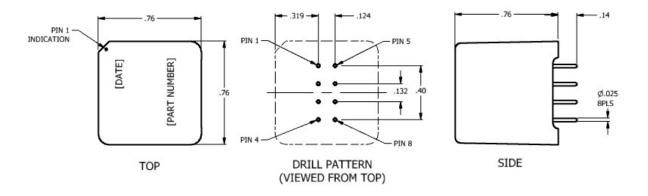

NOTES:

- 1) Unless otherwise noted, all dimensions are in inches. The tolerance is +/- 0.005 for three decimals and +/- 0.010 for two decimals.

- 2) Component Dimensions shown in this figure are for solderable OECs only.

- 3) For OECs installed in enclosures defined by MIL-PRF-22885/108, /113 and /116, dimensions, pin size, pin nomenclature, pin spacing, and component size is determined by enclosure type and the compatibility to the corresponding Common Termination System (CTS).

FIGURE 3. Series N OEC, Solderable.

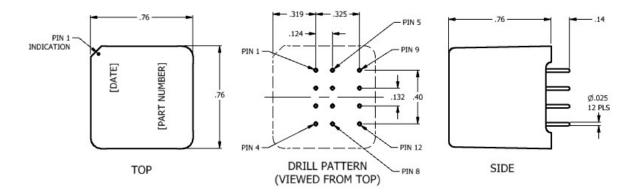

NOTES:

- 1) Unless otherwise noted, all dimensions are in inches. The tolerance is +/- 0.005 for three decimals and +/- 0.010 for two decimals.

- 2) Component Dimensions shown in this figure are for solderable OECs only.

- 3) For OECs installed in enclosures defined by MIL-PRF-22885/108, /113 and /116, dimensions, pin size, pin nomenclature, pin spacing, and component size is determined by enclosure type and the compatibility to the corresponding Common Termination System (CTS).

NOTES:

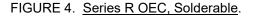

- 1) Housing and Cover are not required for OECs installed in enclosures defined by MIL-PRF-22885/108, /113 and /116.

- 2) Electronic PCB assembly, functional and electrical characteristic of Solderable OEC and OEC inside MIL-PRF-22885/108, /113 and /116 are the same.

FIGURE 5. Generic Exploded view of the assembly.

| Operating info<br>in Tables | Optional Electronic Component<br>(OEC) Function | Series    | Mfg. ID  | Mil<br>ID | Extended<br>ID             |

|-----------------------------|-------------------------------------------------|-----------|----------|-----------|----------------------------|

| II thru IV                  | Solid State Relay                               | A         | SSR      | SR        | 1H<br>1M<br>1L<br>2H<br>2M |

|                             |                                                 |           |          |           | 21VI<br>2L                 |

| V thru VIII                 | Combination- Solid State Relay <u>1/</u>        | С         | SSRC     | CR        |                            |

| IX thru XI                  | Voltage Sensor <u>1/</u>                        | A         | VS       | VS        | A<br>B                     |

| XII thru XIV                | Diode Pack                                      | A         | DP       | DP        | C<br>M                     |

| XV, XVI                     | Terminal Block                                  | Α         | ТВ       | ТВ        |                            |

| XVII thru XXI               | Electronic Latch                                | С         | EL       | EL        | 1 2                        |

| XXII thru XXVI              | Electronic Rotary                               | С         | ER1      | ER        | 1                          |

| XXVII thru XXXI             | Pulse Timer <u>1/</u>                           | С         | PT1      | PT        | 1                          |

| XXXII thru<br>XXXIV         | Current Sensor <u>1/</u>                        | А         | CS       | CS        |                            |

| XXXV thru<br>XXXVIII        | Time Delay <u>1/</u>                            | A         | TD       | TD        | 1 2                        |

| XXXIX thru XLII             | Square Wave Oscillator <u>1/</u>                | A         | СТ       | СТ        | 1 2                        |

| XLIII thru L                | Defined Logic 1/                                | С         | DL       | DL        | 1 2                        |

|                             | <u>0</u> <u></u>                                |           |          | _         | 3                          |

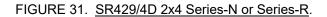

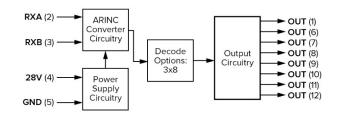

|                             | ARINC Single-Bit Converter <u>1/</u>            | N         | SR429/1M | SC        | <u>т</u>                   |

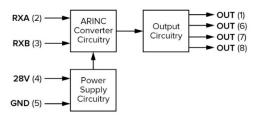

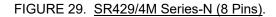

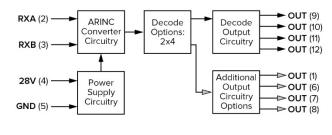

| LI thru LVI                 | ARINC Multi-Bit Converter <u>1/ 2/</u>          | N or<br>R | SR429/4M | МС        |                            |

|                             | ARINC Multi-Bit Binary Decoder <u>1/ 2/</u>     | N or<br>R | SR429/4D | MD        |                            |

## TABLE I. Optional Electronic Components (OECs).

<u>1/</u> These OEC have configurable options after the Extended ID that will only be reflected on manufacturer part numbers.

<u>2/</u> These OEC can be series N or R depending of the outputs.

# Solid State Relay (single), Specifications:

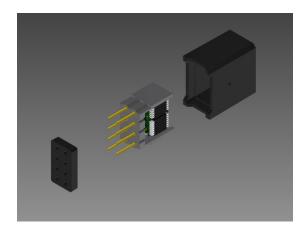

Solid State Relays (SSR) are Series-A (4 Pin) components. SSR allows custom digital and analog signal control, as well as audio and data transitions.

The SSR electrical circuit includes Signal Buffering, Optical Isolation, and Surge-Suppression, between inputs and outputs, to provide control circuit isolation and to protect it from load transients. The SSR control circuit is bridge rectified and therefore bi-directional, allowing DC voltages to be applied in either polarity. See Figure 6.

|                                                                                   | 28 VDC | 14 VDC | 5 VDC |

|-----------------------------------------------------------------------------------|--------|--------|-------|

| Normally Open (NO):<br>0.75 Amp (Resistive) max output load capacity 1/           | SSR1H  | SSR1M  | SSR1L |

| Normally Closed (NC):<br>0.25 Amp (Resistive) max output load capacity <u>1</u> / | SSR2H  | SSR2M  | SSR2L |

| TABLE II. | Configuration | (SSR). |

|-----------|---------------|--------|

|           |               |        |

1/ The outputs switch up to 32 VDC or 28 VAC RMS and are surge-protected against transients and overload conditions via a MOV and fast-blow fuse. 1.6 A for Normally Open and 0.5 A for normally Close.

# FIGURE 6. SSR.

|                           | -             |               |               |

|---------------------------|---------------|---------------|---------------|

|                           | SSR1H/SSR2H   | SSR1M/SSR2M   | SSR1L/SSR2L   |

| Max. Voltage ON           | 32 VDC        | 18 VDC        | 6 VDC         |

| Nominal Voltage ON        | 28 VDC        | 14 VDC        | 5 VDC         |

| Min. Voltage ON           | 18 VDC        | 8 VDC         | 4 VDC         |

| Voltage Off (max)         | +6 VDC        | +4 VDC        | +2 VDC        |

| Typical Operating Current | 6.3 mA        | 6.2 mA        | 12.1 mA       |

| Typical Input Impedance   | 4.4Kohms      | 2.2Kohms      | 400 ohms      |

| Turn On Time Max          | 5 ms / 1 ms   | 5 ms / 1 ms   | 5 ms / 1 ms   |

| Turn Off Time Max         | 0.5 ms / 3 ms | 0.5 ms / 3 ms | 0.5 ms / 3 ms |

TABLE III. Input Parameters (SSR).

### TABLE IV. Output Parameters and Load Capacity (SSR) 1/.

|                           | SSR1 (NO)                   | SSR2 (NC)                   |

|---------------------------|-----------------------------|-----------------------------|

| Max. Output Voltage       | 32 VDC or                   | 28 VAC                      |

| Min. Output Voltage       | N/A                         |                             |

| Loads (AC/DC):            |                             |                             |

| On Resistance             | Typical 0.2-ohm Max 0.5 ohm | Typical 1.0-ohm Max 2.5 ohm |

| Resistive                 | 0.75 A                      | 0.25 A                      |

| Inductive                 | 0.5 A (300mH)               | 0.25 A (300mH)              |

| Lamp                      | 0.1 A(1A, 10ms. Inrush)     | N/A                         |

| Audio                     | < 600 ohms                  |                             |

| Temperature Operating     | -55 C to                    | 85 C                        |

| Temperature Non-Operating | -55 C to                    | 85 C                        |

<u>1/</u>Load tests performed at +85° C.

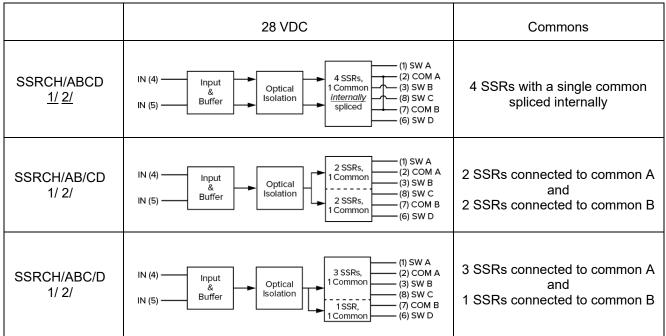

## Combination- Solid State Relay (SSR-C), Specifications:

Combination-Solid State Relays (SSR-C) are Series-C (8 Pin) components. SSR-C shall allow three switching configurations with multiple combinations of Normally Open (NO) and Normally Closed (NC) relays.

# TABLE V. Configurations (SSR-C).

1/ Each character of ABCD is replaced with either 1 for NO (Normally Open) or 2 for NC (Normally close) depending on switching options.

2/ Output load capacity differential for NO and NC must be consider when using in same configuration.

|                           | Parameter |

|---------------------------|-----------|

| Max. Voltage ON           | 32 VDC    |

| Nominal Voltage ON        | 28 VDC    |

| Min. Voltage ON           | 18 VDC    |

| Voltage Off (max)         | +6 VDC    |

| Typical Operating Current | 25 mA     |

| Typical Input Impedance   | 1.1 Kohms |

| Turn On Time Max          | 5 ms      |

| Turn Off Time Max         | 3 ms      |

### TABLE VI. Input Parameters (SSR-C).

# TABLE VII. Output Parameters and Load Capacity (SSR-C). 1/

|                           | SSR1 (NO)                   | SSR2 (NC)                   |

|---------------------------|-----------------------------|-----------------------------|

| Max. Output Voltage       | 32 VDC or                   | 28 VAC                      |

| Min. Output Voltage       | N/A                         |                             |

| Loads (AC/DC):            |                             |                             |

| On Resistance             | Typical 0.2-ohm Max 0.5 ohm | Typical 1.0-ohm Max 2.5 ohm |

| Resistive                 | 0.75 A                      | 0.25 A                      |

| Inductive                 | 0.5 A (300mH)               | 0.25 A (300mH)              |

| Lamp                      | 0.1 A(1A, 10ms. Inrush)     | N/A                         |

| Audio                     | < 600 ohms                  |                             |

| Temperature Operating     | -55 C to                    | 85 C                        |

| Temperature Non-Operating | -55 C to                    | 85 C                        |

1/ Load tests performed at +85° C.

# TABLE VIII. Signal Description.

| Signals                                 | Logic Functions Normally Open<br>(SSR1)                         | Logic Functions Normally Closed (SSR2)                       |

|-----------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------|

| SW A, SW B, SW<br>C, and SW D <u>2/</u> | Shorted to COM A or COM B when the inputs (IN) are Active       | Shorted to COM A or COMB when the inputs (IN) are not Active |

| Common                                  | Signal COM A and COM B                                          |                                                              |

| IN                                      | Active when +28 VDC is applied across the inputs (IN) <u>1/</u> |                                                              |

Notes

$\underline{1}$ / Input control circuits are bridge rectified and will respond to current flowing in either direction. Applications with reverse polarity sneak paths will require an external polarity protection diode.  $\underline{2}$ / Outputs (A, B, C, and D) fused at 1.6 A and 0.5 A to protect against transients and overload conditions.

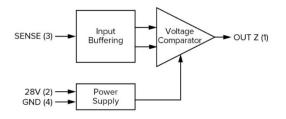

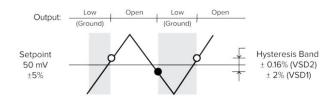

### **OEC Voltage Sensor (VS), Specifications:**

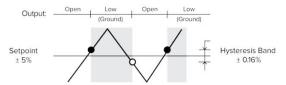

Voltage Sensor is a solid- state, low-side direct current (DC) voltage sensor and may be configured for undervoltage or overvoltage detection. Voltage sensing is low drift over the specified temperature range. The Voltage Sensor compares positive DC voltage in a linear relationship between the specified setpoint and the voltage that is being monitored by the Sense Input (Pin 3). The OUT Z (Pin 1) provides a discrete signal that transitions from Open to Ground when the Sense Input (Pin 3) detects voltage that is above or below the specified setpoint. See Figure 7.

FIGURE 7. Voltage Sensor.

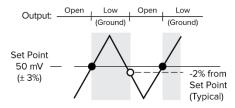

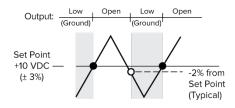

| Туре         | Voltage Ser             | nse Values | Open Drain Output OUT Z<br>(Pin 1) |                              | Tolerances <u>1</u> / <u>2</u> /                                                          |

|--------------|-------------------------|------------|------------------------------------|------------------------------|-------------------------------------------------------------------------------------------|

|              | Range                   | Increments | Active                             | Not Energized<br>or inactive |                                                                                           |

|              | 50 to 90<br>mV          | 10mVDC     |                                    |                              | Nominal tolerance of a specified setpoint is +/-                                          |

| VSD2         | 100 to<br>1000 mV<br>DC | 50mVDC     |                                    |                              | 5%. Voltage hysteresis<br>band of +/- 1% around<br>the setpoint, See<br>Figures 10 and 11 |

|              | 1 to 9 VDC              | 0.5 VDC    | Ground                             | High<br>Impedance            | Nominal Rising Voltage                                                                    |

|              | 10 to 30<br>VDC         | 1 VDC      |                                    | (Open)                       | Set Point Tolerance +/-<br>5%. Falling Voltage                                            |

| VSD1         | 32 to<br>40VDC          | 2 VDC      |                                    |                              | Hysteresis -3% Max (-<br>2% Typical). See                                                 |

| 4/104-2-2-20 | 44 to 48<br>VDC         | 4 VDC      |                                    |                              | Figure 8 and 9.                                                                           |

| TARI E IX  | Configuration | (Voltage Sensor). |  |

|------------|---------------|-------------------|--|

| I ADLE IA. | Configuration | (vollage Sensor). |  |

1/ Measured from the Set Point after the inclusion of the Rising Voltage Set Point Tolerance above.  $\frac{1}{2}$ / Tolerance of EMC and Environmental extremes is 10%.

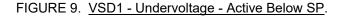

FIGURE 8. VSD1 - Overvoltage - Active Above SP.

FIGURE 10. VSD2 - Overvoltage - Active Above SP.

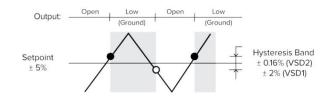

FIGURE 11. VSD2 - Undervoltage - Active Below SP.

| Description                                                                                                                         | Parameters                |

|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Power                                                                                                                               | Parameters                |

| Minimum Operating Voltage                                                                                                           | +18 VDC                   |

| Maximum Operating Voltage                                                                                                           | +32 VDC                   |

| Power Supply Current                                                                                                                | 2 mA Max.                 |

| Reset From Power Loss                                                                                                               | 5 second minimum @ +25° C |

| Hold Up On Power Loss                                                                                                               | 200 ms minimum            |

| Input                                                                                                                               | Parameters                |

| Minimum Sense Voltage                                                                                                               | See range at Table IX     |

| Maximum Sense Voltage                                                                                                               | See range at Table IX     |

| Rising Voltage Set Point Tolerance                                                                                                  | See Tolerance at Table IX |

| Falling Voltage Hysteresis<br>Note: Measured from the Set Point after inclusion of<br>the Rising Voltage Set Point Tolerance above. | See Tolerance at Table IX |

| Transition Time Sense to Out (TSense)                                                                                               | 5 ms Max.                 |

| Input Impedance to unit ground                                                                                                      | >1 Mohm                   |

# TABLE X. Power and Input Parameters (Voltage Sensor).

TABLE XI. Output Parameters and Load Capacity (Voltage Sensor). 1/

| Output Parameters                                    | VSD1 Output Parameters | VSD2 Output Parameters |  |

|------------------------------------------------------|------------------------|------------------------|--|

| Static Drain-Source On-State<br>Resistance (RDS(ON)) | 48 mohm                | 600 mohm               |  |

| Maximum Load (Resistive)                             | 2.0 A                  | 0.5 A                  |  |

| Maximum Load (Inductive)                             | 0.8 A (300mH)          | 0.5 A (300mH)          |  |

|                                                      | Temperature            |                        |  |

| Operating                                            | -55° C to              | +85° C                 |  |

| Non-operating                                        | -55° C to +85° C       |                        |  |

$\underline{1}$ /Load tests performed at +85° C.

# Diode Pack (DP), Specifications:

Diode Pack (DP) are Series-A (4 Pin) components. Each Diode Pack component contains two independent diode circuits. See Figure 12.

FIGURE 12. Diode Pack.

| TABLE XII. | Configuration | (Diode Pack). |

|------------|---------------|---------------|

|            |               |               |

|                           | DP2C                    | DP2M                         |

|---------------------------|-------------------------|------------------------------|

| Internal Didoes <u>1/</u> | 1N6484                  | 1N5621JANTX                  |

|                           | glass passivized diodes | Hermetic glass sealed diodes |

1/ Consult manufacturer's data sheet for detailed diode specifications.

## TABLE XIII. Insulation Parameters (Diode Pack).

|                         | DP2C DP2M             |

|-------------------------|-----------------------|

| Insulation Resistance   | 5000 Megaohms @ 25° C |

| Dielectric Withstanding | 1000 VRMS             |

TABLE XIV. Electrical Parameters (Diode Pack). 1/

|                           | DP2C      | DP2M          |

|---------------------------|-----------|---------------|

| Current Rating (maximum)  | 1 Amp     | 1 Amp         |

| Reverse Working Voltage   | +1000 VDC | +800 VDC      |

| Reverse Breakdown Voltage | +1000 VDC | +880 VDC Peak |

| Temperature Operating     | -55 C 1   | to 85 C       |

| Temperature Non-Operating | -55 C 1   | to 85 C       |

# Terminal Block (TB), Specifications:

Terminal Block (TB) are Series-A (4 Pin) components. Each Terminal Block has a maximum of 5 Amps rating and provides the ability to buss a single input to three outputs. See Figure 13.

FIGURE 13. Single Configuration TB4.

| TABLE XV. | Insulation Parameters | (Terminal Block). |

|-----------|-----------------------|-------------------|

|           |                       |                   |

|                         | ТВ                    |

|-------------------------|-----------------------|

| Insulation Resistance   | 5000 Megaohms @ 25° C |

| Dielectric Withstanding | 1000 VRMS             |

## TABLE XVI. Electrical Parameters (Terminal Block).

|                           | TB            |

|---------------------------|---------------|

| Current Rating (maximum)  | 5 Amp         |

| Temperature Operating     | -55 C to 85 C |

| Temperature Non-Operating | -55 C to 85 C |

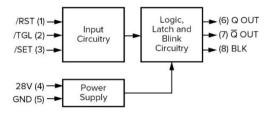

# Electronic Latch (EL) , Specifications:

Solid State Electronic Latch (EL1, EL2), a Series-C (8 Pin) component, provides switching between orthogonal states.

EL1, EL2 input circuitry shall be diode isolated, buffered, and debounced. EL1, EL2 outputs shall be active ground open drain drivers both fused and surge-protected against transients and overload conditions.

EL1, EL2 provides two different operating modes by activating /SET, /RST, or /TGL. The switch then responds with conditioned outputs.

Latching circuitry holds the current state and provides /SET, /RST, and /TGL features along with a built-in blink (BLK) (1 Hz square wave) capability. See Figure 14.

|             |        | EL1          | EL2                                                                                      |

|-------------|--------|--------------|------------------------------------------------------------------------------------------|

| Power Up in |        | Reset        | Set                                                                                      |

|             | Q OUT  | High (Open)  | Low (Ground)                                                                             |

|             | /Q OUT | Low (Ground) | High (Open)                                                                              |

| At Power up | BLINK  | OFF (Open)   | 1 Hz (50% duty cycle) square<br>wave alternating between High<br>(Open) and Low (Ground) |

| TABLE XVII. Configuration (Electronic Latch). |

|-----------------------------------------------|

|-----------------------------------------------|

FIGURE 14. Electronic Latch.

| Pin<br>Ref | Signal<br>Name | Function | Input Trigger or<br>Active State | Description                                                                                                                          |

|------------|----------------|----------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1          | /RST           | Input    | Low (Ground)                     | Forces Q OUTPUT to OFF (Open). Forces /Q OUT to ON (Ground). Forces BLK to Steady ON (Ground). <u>1/</u>                             |

| 2          | /TGL           | Input    | <u>− 3</u> /                     | Toggles Q OUT and /Q OUT. Toggles blink mode. <u>2/</u>                                                                              |

| 3          | /SET           | Input    | Low (Ground)                     | Forces Q OUT to ON (Ground). Forces /Q OUTPUT to OFF (Open). Initiates the 1Hz blink mode to BLINK Output.                           |

| 4          | +28V           | Power    | _                                | Power (+18 VDC to +32 VDC)                                                                                                           |

| 5          | GND            | Common   | _                                | Continuous Ground Required.                                                                                                          |

| 6          | Q OUT          | Output   | Low (Ground)                     | Open Drain Output. Forced OFF (Open) by /RST<br>Input. Forced ON (Ground) by /SET Input. Toggled<br>by Falling Edge of /TGL Input.   |

| 7          | /Q OUT         | Output   | Low (Ground)                     | Open Drain Output. Forced ON (Ground) by /RST<br>Input. Forced OFF (Open) by /SET Input. Toggled by<br>Falling Edge of /TOGGLE Input |

| 8          | BLK            | Output   | Low (Ground)                     | Open Drain Output. Forced ON (Ground) while<br>/RST is held Low (Ground).                                                            |

1/ BLK Output is held Steady ON (Ground) while /RST is held low. BLK Output goes OFF (Open) when /RESET returns to the inactive high level. This feature provides essentially three states to the BLINK Output: OFF, ON, and BLK. During EL1 Power-Up, /RESET is held low momentarily, which may result in a flicker of the indicator.

2/ TOGGLE input causes BLINK Output to switch between 1 Hz Blink state and OFF (Open). /TGL is overridden by /RST or /SET if they are active.

3/ Momentary toggle from High (Open) to Low (Ground) will flop Q OUT & /Q OUT to the opposite state.

|                            | EL1 / EL2                 |

|----------------------------|---------------------------|

| Maximum Operating Voltage  | +32 VDC                   |

| Nominal Operating Voltage  | +28 VDC                   |

| Minimum Operating Voltage  | +18 VDC                   |

| Power Supply Input Current | 4 mA maximum              |

| Reset From Power Loss      | 5 second minimum @ +25° C |

| Hold Up On Power Loss      | 50 ms minimum             |

TABLE XIX. Power Parameters (Electronic Latch).

TABLE XX. Input Parameters @ 25C (Electronic Latch). 1/

|                                  | EL1 / EL2       |

|----------------------------------|-----------------|

| EL1: /RST, EL2: /SET             | 120 ms minimum  |

| /TGL                             | 45 ms minimum   |

| EL1: /SET, EL2: /RST             | 45 ms minimum   |

| High Level Input Voltage ( VIH ) | 3 VDC minimum   |

| Low Level Input Voltage ( VIL )  | 0.4 VDC maximum |

| Low Level Input Current ( IIL )  | 1 mA maximum    |

<u>1</u>/ All signal inputs are diode isolated

| TABLE XXI. Output Parameters and Load Capacity (Electronic Latch) |

|-------------------------------------------------------------------|

|-------------------------------------------------------------------|

|                                 | EL1 / EL2     |

|---------------------------------|---------------|

| Loads:                          |               |

| Resistive                       | 2.0 A         |

| Motor                           | 1.0 A         |

| Lamp                            | 0.8 A         |

| Inductive                       | 0.8 A (300mH) |

| Temperature Operating           | -55 C to 85 C |

| Temperature Non-Operating       | -55 C to 85 C |

| 1/1 and toota parformed at +95° | <u></u>       |

<u>1</u>/Load tests performed at +85° C.

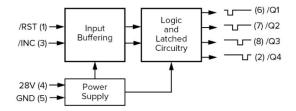

# Electronic Rotary (ER1), Specifications:

Electronic Rotary (ER1), a Series-C (8 Pin) component, provides incremental switching through up to four latched output states. The number of latched states is user-defined and determined by routing the next highest output state back to the /RST input.

ER1 input circuitry shall be diode isolated, buffered, and debounced. ER1 outputs shall be Active ground open drain drivers both fused and surge-protected against transients and overload conditions.

The latching circuitry holds the current state until /INC or /RST inputs are toggled from High (Open) to Low (Ground). See Figure 15.

|             |     | ER1          |

|-------------|-----|--------------|

|             | /Q1 | Low (Ground) |

| At Power up | /Q2 | High (Open)  |

|             | /Q3 | High (Open)  |

|             | /Q4 | High (Open)  |

TABLE XXII. Configuration (Electronic Rotary).

FIGURE 15. Electronic Rotary.

| TABLE XXIII. Signals Description (Electronic Rotary). | TABLE XXIII. | Signals Description | (Electronic Rotary). |

|-------------------------------------------------------|--------------|---------------------|----------------------|

|-------------------------------------------------------|--------------|---------------------|----------------------|

| Pin<br>Ref | Signal<br>Name | Function                                                                           | Active<br>State                                               |

|------------|----------------|------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 1          | /RST           | Input Low-Resets to state 1 with /Q1<br>latched low when held low                  |                                                               |

| 2          | /Q4            | Output: Default=High impedance (Open Drain)<br>Becomes ground when state is active |                                                               |

| 3          | /INC           | High to low transition advances the unit to the next state                         | Increment input at state 4 will return the<br>unit to state 1 |

| 4          | +28V           | Power                                                                              |                                                               |

| 5          | GROUND         | Ground                                                                             | Cont. Ground Req'd                                            |

| 6          | /Q1            | Output: High impedance (Open Drain)<br>Becomes ground when state is active         |                                                               |

| 7          | /Q2            | Output: Default=High impedance (Open Drain)<br>Becomes ground when state is active |                                                               |

| 8          | /Q3            | Output: Default=High impedance (Open Drain)<br>Becomes ground when state is active |                                                               |

TABLE XXIV. Power Parameters (Electronic Rotary).

|                            | ER1                      |

|----------------------------|--------------------------|

| Maximum Operating Voltage  | +32 VDC                  |

| Nominal Operating Voltage  | +28 VDC                  |

| Minimum Operating Voltage  | +18 VDC                  |

| Power Supply Input Current | 4 mA maximum             |

| Reset From Power Loss      | 5 second minimum @ +25°C |

| Hold Up On Power Loss      | 50 ms minimum            |

|                                 | ER1             |

|---------------------------------|-----------------|

| /INC                            | 50 ms minimum   |

| /RST                            | 80 ms minimum   |

| Timing /INC to output           | 100 ms maximum  |

| High Level Input Voltage(VIH)   | 3 VDC minimum   |

| Low Level Input Voltage ( VIL ) | 1.2 VDC maximum |

| Low Level Input Current ( IIL ) | 1 mA maximum    |

TABLE XXV. Input Parameters at 25°C (Electronic Rotary). 1/

<u>1/</u> All signal inputs are diode isolated

TABLE XXVI. Output Parameters and Load Capacity (Electronic Rotary). 1/

|                                 | ER1           |

|---------------------------------|---------------|

| Loads:                          |               |

| Resistive                       | 2.0 A         |

| Motor                           | 1.0 A         |

| Lamp                            | 0.8 A         |

| Inductive                       | 0.8 A (300mH) |

| Temperature Operating           | -55 C to 85 C |

| Temperature Non-Operating       | -55 C to 85 C |

| 1/L and toota performed at +95° | C             |

1/ Load tests performed at +85° C.

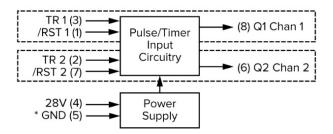

## Pulse Timer (PT1), Specifications:

Pulse Timer (PT1) is a Series-C (8 Pin) dual-channel edge detector and pulse generator. Each channel is independent and provides stable retriggerable/resettable one-shot operation for fixed timing applications. The trigger inputs allow rise and fall times that can be specified to sense either a rising-edge (Low to High) or falling-edge (High to Low) transition.

The PT1 can generate a wide range of timed pulse widths that are specified as either active High (Open) or active Low (Ground). Each channel includes a Low-triggered Reset Input for immediate termination of the pulsed Output.

PT1 input circuitry shall be diode isolated, buffered, and debounced. PT1 outputs shall be Active ground open drain both fused and surge-protected against transients and overload conditions.

The inputs must include an internal pull up to approximately +18 VDC. The PT1 requires constant power (+28 VDC) and Ground for proper operation. See Figure 16.

|     | Trigger      | Outputs         | Pulse length options<br>(+/- 10% at +25°C) |

|-----|--------------|-----------------|--------------------------------------------|

|     | Positive (P) | Active High (H) | 125 ms,<br>250 ms,                         |

|     |              | Active Low (L)  | 500 ms,<br>1 sec                           |

| PT1 | Negative(N)  | Active High (H) | 2.5 sec<br>5 sec                           |

|     |              | Active Low (L)  | 10 sec<br>20 sec                           |

TABLE XXVII. Configuration (Pulse Timer) 1/.

1/ Each of the two independent channels can be configure as per the table.

FIGURE 16. Pulse Timer.

# TABLE XXVIII. Power Parameters (Pulse Timer).

|                                        | PT1                         |

|----------------------------------------|-----------------------------|

| Operating Voltage (Max. / Nom. / Min.) | +32 VDC / +28 VDC / +18 VDC |

| Power Supply Input Current             | 4 mA maximum                |

| Reset From Power Loss                  | 5 second minimum @ +25°C    |

| Hold Up On Power Loss                  | 200 ms minimum              |

|--|

|                      |                          |                          | Output Response                                                             |                                                                             |  |  |

|----------------------|--------------------------|--------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| Input                | Selected Input<br>Option | Actual Input<br>Received | Q1 or Q2 Active High<br>(Open) Normally Low                                 | Q1 or Q2 Active Low<br>(Ground) Normally High<br>T                          |  |  |

|                      | Rising<br>(Positive)     | Rising (Positive)<br>_r  | Output transitions from<br>Ground to Open for the<br>specified pulse period | Output transitions from Open<br>to Ground for the specified<br>pulse period |  |  |

| TR 1 or              | Edge<br>Detecting        | Falling (Negative)       | No Change: Output remains at Ground                                         | No Change: Output remains<br>at Open                                        |  |  |

| TR2                  | Falling<br>(Negative)    | Rising (Positive)        | No Change: Output remains at Ground                                         | No Change: Output remains<br>at Open                                        |  |  |

|                      | Edge<br>Detecting        | Falling (Negative)       | Output transitions from<br>Ground to Open for the<br>specified pulse period | Output transitions from Open<br>to Ground for the specified<br>pulse period |  |  |

|                      | -                        | Reset = Open             | Q1 and Q2 operate as defined above                                          |                                                                             |  |  |

| /RST 1 or<br>/RSET 2 | -                        | Reset = Ground           | Output is disabled (pulse<br>cancelled) and is held at<br>Ground            | Output is disabled (pulse cancelled) and is held Open                       |  |  |

|                                 | PT1             |

|---------------------------------|-----------------|

| /RESET (/RST)                   | 55 ms minimum   |

| TRIGGER (TR 1) (TR 2)           | 40 ms minimum   |

| High Level Input Voltage(VIH)   | 5 VDC minimum   |

| Low Level Input Voltage ( VIL ) | 1.2 VDC maximum |

| Low Level Input Current ( IIL ) | 1mA maximum     |

TABLE XXX. Input Parameters at 25°C (Pulse Timer). 1/.

1/ All signal inputs are diode isolated

TABLE XXXI. Output Parameters and Load Capacity (Pulse Timer). 1/

|                                  | PT1           |  |

|----------------------------------|---------------|--|

|                                  | PII           |  |

| Loads:                           |               |  |

| Resistive                        | 2.0 A         |  |

| Motor                            | 1.0 A         |  |

| Lamp                             | 0.8 A         |  |

| Inductive                        | 0.8 A (300mH) |  |

| Temperature Operating            | -55 C to 85 C |  |

| Temperature Non-Operating        | -55 C to 85 C |  |

| 1/Load tests performed at +85° C |               |  |

<u>1</u>/ Load tests performed at +85°

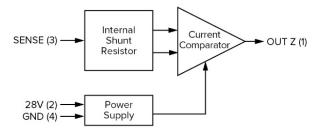

## **Current Sensor (CS), Specifications:**

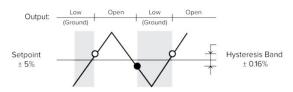

Current Sensor (CS) is a solid-state, low-side direct current sensor. May be configure for undercurrent or overcurrent detection.

The CS compares electric current in a linear relationship between the specified setpoint and the current that is being monitored by the Sense Input. The output (OUT Z) provides a discrete signal that transitions from Open to Ground when the Sense Input detects current that is above or below the specified set point. See Figure 17.

FIGURE 17. Current Sensor.

|      |            |                     | Open Drai | n Output (Pin 1)             |                                              |                                                                |

|------|------------|---------------------|-----------|------------------------------|----------------------------------------------|----------------------------------------------------------------|

| Туре | Increments | Range               | Active    | Not Energized<br>or inactive | Tolerances <u>1</u> /                        |                                                                |

|      | 10mA DC    | 10 to 90<br>mA DC   |           | High                         | Nominal tolerance of a specified setpoint is |                                                                |

| CS1  | 50mA DC    | 50 to 1000<br>mA DC | Ground    | Ground                       | Impedance<br>(Open)                          | +/- 5%. Hysteresis<br>band of +/- 1% See<br>Figures 17 and 18. |

TABLE XXXII. Configuration (Current Sensor).

1/ Tolerance of specified Set Point is +/-10% at EMC and Environmental extremes.

FIGURE 18. CS1 Overcurrent - Active Above SP

FIGURE 19. CS1 Undercurrent - Active Below SP

|--|

| Description                           | Parameters                      |  |

|---------------------------------------|---------------------------------|--|

| Power Parameters                      |                                 |  |

| Operating Voltage (Max./Nom./ Min.)   | +32 VDC /+28 VDC/+18 VDC        |  |

| Power Supply Input Current            | 4 mA maximum                    |  |

| Reset From Power Loss                 | 5 second minimum @ +25°C        |  |

| Hold Up On Power Loss                 | 50 ms minimum                   |  |

| Input Timing Input Impedance          | 10 ms maximum Approx. 100K Ohms |  |

| Input Par                             | ameters                         |  |

| Minimum Sense Current                 | See Table XXXII                 |  |

| Maximum Sense Current                 | See Table XXXII                 |  |

| Transition Time Sense to Out (TSense) | 5 ms maximum                    |  |

| Output Parameters               | Output Parameters                             |

|---------------------------------|-----------------------------------------------|

| Low Level Output                | +0.4 VDC typical, +0.6 VDC maximum            |

| High Level Output Voltage (VOH) | Open Drain<br>+32 VDC maximum pull-up allowed |

| Maximum Load (Resistive)        | 0.5 A                                         |

| Maximum Load (Inductive)        | 0.5 A (300mH)                                 |

| Tempe                           | rature                                        |

| Operating                       | -55° C to +85° C                              |

| Non-operating                   | -55° C to +125° C                             |

TABLE XXXIV. Output Parameters and Load Capacity (Current Sensor). 1/

1/ Load tests performed at +85° C.

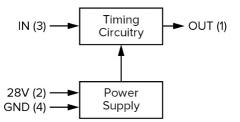

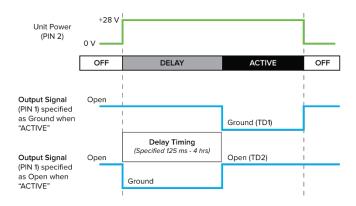

# Time Delay (TD), Specifications:

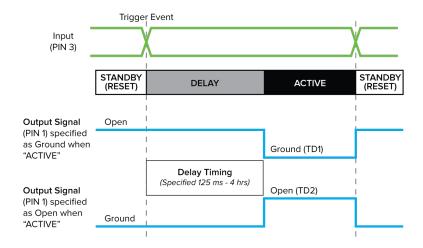

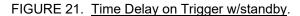

Time Delay (TD1, TD2) is a Series-A (4-Pin) device with a range of timing options. The Input may be specified to detect a logic level (High/Low) as the event which triggers the Output to start the delay timer. Time Delay may also be specified to start the delay timer upon power-up. See Figure 20.

| TABLE XXXV. Configuration (Time Delay). 1/ |  |

|--------------------------------------------|--|

|--------------------------------------------|--|

| Outputs                             | Time Delay<br>starts  | Stand-<br>by | Delay Timing Options<br>(+/- 5% at +25°C) 4/                                       |

|-------------------------------------|-----------------------|--------------|------------------------------------------------------------------------------------|

| TD1<br>(Ground when Active and      | At Power UP <u>3/</u> | Yes          | •Milliseconds: 125*, 250*, 500 ms (*not available with the Time Delay on Power-up) |

| Open when in Standby or<br>Delay)   | On Trigger <u>2/</u>  | -            | •Seconds: 1, 2, 3, 4, 5, 6, 7, 8, 9, 10,<br>15, 20, 30 sec                         |

| TD2<br>(Open when Active and        | At Power UP <u>3/</u> | Yes          | •Minutes: 1, 2, 3, 4, 5, 6, 7, 8, 9, 10,<br>15, 20, 30 min                         |

| Ground when in<br>Standby or Delay) | On Trigger <u>2/</u>  | -            | •Hours: 1, 2, 4 hrs                                                                |

1/ Each of the two independent channels can be configure as per the table.

<u>2</u>/ See Figures 20 and 21<u>.</u> <u>3</u>/ See Figures 22<u>.</u>

4/ Tolerance of timing over temperature and EMC +/- 10%.

| Transition Options for INPUT Level          |                                                |  |

|---------------------------------------------|------------------------------------------------|--|

| STANDBY                                     | DELAY/ACTIVE                                   |  |

| +28 VDC or Open                             | Ground                                         |  |

| +28 VDC<br>Must be same power source as PWR | Ground or Open                                 |  |

| Ground or Open                              | +28 VDC<br>Must be same power source as<br>PWR |  |

| Ground                                      | +28 VDC or Open                                |  |

| FIGURE 22. Transition Options. |

|--------------------------------|

|--------------------------------|

FIGURE 23. Time Delay on Power Up.

|                                           | TD                          |

|-------------------------------------------|-----------------------------|

| Operating Voltage<br>(Max. / Nom. / Min.) | +32 VDC / +28 VDC / +18 VDC |

| Power Supply Input Current                | 4 mA maximum                |

| Reset From Power Loss                     | 5 second minimum @ +25°C    |

| Hold Up On Power Loss                     | 200 ms minimum              |

### TABLE XXXVI. Power and input Parameters (Time Delay).

# TABLE XXXVII. Input Parameters at 25° C (Time Delay). 1/

| TD            |

|---------------|

| 10 ms maximum |

| 1 mA maximum  |

| < +1.5 VDC    |

| > +8 VDC      |

|               |

<u>1</u>/ All signal inputs are diode isolated.

## TABLE XXXVIII. Output Parameters and Load Capacity. 1/

|                                     | TD                         |

|-------------------------------------|----------------------------|

| Low Level Output Voltage @ 1A (VOL) | +0.4 VDC typical, +0.6 VDC |

|                                     | maximum                    |

| High Level Output Voltage (VOH)     | Open                       |

|                                     | Drain                      |

|                                     | +32 VDC maximum            |

|                                     | pull-up allowed            |

| Loads:                              |                            |

| Resistive                           | 0.5 A Max                  |

| Lamp/Incandescent                   | 0.5 A                      |

| Inductive                           | 0.5 A (300mH)              |

| Temperature Operating               | -55° C to 85° C            |

| Temperature Non-Operating           | -55° C to 125° C           |

$\underline{1}$ /Load tests performed at +85° C.

# Square Wave Oscillator (CT) , Specifications:

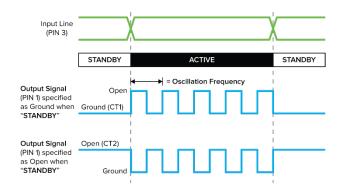

Square Wave Oscillator (CT1, CT2) is a Series-A (4-Pin) device with a range of oscillation frequency options. The Input may be specified to detect a logic level (High/Low) as the event which triggers the Output to begin oscillating. The Output continue oscillating until the trigger condition is reversed. See Figure 24 and Figure 25.

CT1, CT2 includes input circuity that is diode isolated, buffered, and debounced to provide reliable operation. The Output (Pin 1) is a High/Low (Open/Ground) driver that is fused and surge-protected against transients and overload conditions.

CT1, CT2 input circuitry shall be diode isolated, buffered, and debounced. CT1, CT2 outputs shall be High/Low driver fused and surge-protected against transients and overload conditions.

|     | Out        | lput        | Delay Timing Options<br>(+/- 5% at +25°C) <u>2/</u>                            |

|-----|------------|-------------|--------------------------------------------------------------------------------|

|     | At Standby | When Active | Frequency / Period                                                             |

| CT1 | Ground     | Osc.        | 500 Hz / 0.002 sec<br>100 Hz / 0.01 sec<br>10 Hz / 0.10 sec<br>4 Hz / 0.25 sec |

| CT2 | Open       | Osc.        | 2 Hz / 0.50 sec<br>1 Hz / 1 sec<br>0.5 Hz / 2 sec<br>0.25 Hz / 4 sec           |

| TABLE XXXIX. | Configuration | (Square Wave Oscillator). | 1/ |

|--------------|---------------|---------------------------|----|

|              |               |                           |    |

$\underline{1}$ / Each of the two independent channels can be configure as per the table.

$\frac{2}{}$  Tolerance of timing over temperature and EMC +/- 10%.

FIGURE 24. Square Wave Oscillator circuit.

FIGURE 25. Square Wave Oscillator signal.

| TABLE XL. Power Parameters (Square Wave Oscillator). |

|------------------------------------------------------|

|------------------------------------------------------|

|                                        | СТ                          |

|----------------------------------------|-----------------------------|

| Operating Voltage (Max. / Nom. / Min.) | +32 VDC / +28 VDC / +18 VDC |

| Power Supply Input Current             | 4 mA maximum                |

| Reset From Power Loss                  | 5 second minimum @ +25°C    |

| Hold Up On Power Loss                  | 200 ms minimum              |

| СТ            |

|---------------|

| 10 ms maximum |

| 1 mA maximum  |

| < +1.5 VDC    |

| > +8 VDC      |

|               |

TABLE XLI. Input Parameters at 25°C (Square Wave Oscillator). 1/

1/ All signal inputs are diode isolated.

TABLE XLII. Output Parameters and Load Capacity (Square Wave Oscillator). 1/

|                                     | СТ                              |

|-------------------------------------|---------------------------------|

| Low Level Output Voltage @ 1A (VOL) | +0.4 VDC typical, +0.6 VDC      |

|                                     | maximum                         |

| High Level Output Voltage (VOH)     | Open Drain                      |

|                                     | +32 VDC maximum pull-up allowed |

| Loads:                              |                                 |

| Resistive                           | 0.5 A Max                       |

| Lamp/Incandescent                   | 0.5 A                           |

| Inductive                           | 0.5 A (300mH)                   |

| Temperature Operating               | -55° C to 85° C                 |

| Temperature Non-Operating           | -55° C to 125° C                |

|                                     |                                 |

1/ Load tests performed at +85° C.

### Defined Logic (DL), Specifications:

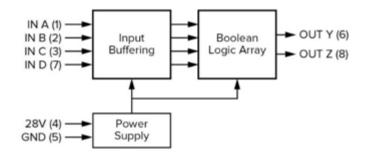

Defined Logic products are Series- C (8-Pin) component. It provides solid-state Boolean Logic control for use with digital circuit design. Each variation includes the ability to monitor up to four discrete inputs and drive two discrete outputs based on a logic decode of the inputs.

The Defined Logic interface handles Logic High and Logic Low levels that can be used to produce traditional Boolean Gates like AND, NAND, OR, NOR, EXOR, EXNOR, and NOT (Inverter).

The internal circuitry also performs the function of a signal Buffer. See Figure 26.

FIGURE 26. Defined Logic.

### Configuration Options:

The Defined Logic (DL) Series consist of four configuration types and standard design characteristics that are common to each. Each Defined Logic configuration is comprised of four inputs (A - D) and two outputs (Y and Z). See Figure 26 and Table XLIII. The options vary among each type, and the following describes the unique characteristics which differentiate the four Defined Logic products.

|     | Inputs<br>A-D          | Outputs                               | Available<br>functions | Functional Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|------------------------|---------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DL1 | two<br>(tied)<br>pairs | two<br>orthogonal                     | TABLE XLIV             | $ \begin{array}{c} I N A \longrightarrow \\ I N C \longrightarrow \\ I N C \longrightarrow \\ I N D \longrightarrow \\ 28V \longrightarrow \\ GND \longrightarrow \\ \end{array} \begin{array}{c} Boolean \\ Logic Array \\ Power \\ Supply \end{array} \rightarrow OUT Y \\ OUT Z=\overline{Y} \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DL2 |                        |                                       | TABLE XLV              | Channel 1 IN A Boolean<br>Channel 2 IN C Channel 2 IN |

| DL3 |                        |                                       | TABLE XLVI             | IN A<br>IN B<br>Logic Gate 1<br>IN C<br>Logic Gate 2<br>OUT T<br>Logic Gate 3<br>OUT Y<br>Logic Gate 3<br>OUT Y<br>OUT Z= $\overline{Y}$<br>IN D<br>28V<br>Power<br>GND<br>Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DL4 | four<br>discrete       | provides two<br>orthogonal<br>outputs | TABLE XLVII            | IN A $\rightarrow$<br>IN B $\rightarrow$<br>IN C $\rightarrow$<br>IN D $\rightarrow$<br>28V $\rightarrow$<br>GND $\rightarrow$<br>Boolean<br>Logic Array<br>Power<br>Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## TABLE XLIII. Configuration types (Defined Logic)

Defined Logic (DL1): Monitor one set of inputs or the other when a signal is detected as active or not active, but not both. The DL1 output levels are specified as Logic High when both pairs of inputs are identical, and Logic Low when the pair of inputs differ.

The DL1 indicates when either one system or another is active or off, but not both. The DL1 will generate an Open (1) signal from output Y when both pairs of inputs are identical, and a Ground (0) signal when one pair is ground and the other pair is High Impedance. Output Z is orthogonal to Output. See Table XLIV.

For the DL1 variant only, input Pins A and C must be specified identically as either Pull-up or Pull-down since they must be externally tied together. Defined Logic (DL1) input options include specifying Pins A and C as Pull-up or Pull-down at the time of part configuration. See Input Level Options for Pins A and C.

|                                       |       | Out      | puts    |  |

|---------------------------------------|-------|----------|---------|--|

| Inp                                   | outs  | ("/XOR") | ("XOR") |  |

| A, C                                  | B , D | Y        | Z       |  |

| 0                                     | 0     | 1        | 0       |  |

| 0                                     | 1     | 0        | 1       |  |

| 1                                     | 0     | 0        | 1       |  |

| 1                                     | 1     | 1        | 0       |  |

| 0 = Ground; 1 = Open (high impedance) |       |          |         |  |

### TABLE XLIV. DL1 Functions.

Defined Logic (DL2): The DL2 consists of dual (two) logically independent channels. Each channel consists of two inputs and a single output that is capable of providing one of ten types of Boolean Logic control. See Table XXXIII and Table XLV.

Defined Logic (DL2) functions:

- 1) Boolean Logic decode (AND/OR/NAND/NOR, Logic Options 1-8), based on specific input level conditions to provide an output, specified as Ground (0) or Open (1),

- 2) Buffer output provides a filtered state of the input level,

- 3) Not (Inverter) output is orthogonal to the input level.

Defined Logic (DL2) input options include specifying Pins A and C as Pull-up or Pull-down at the time of part configuration. See Input Level Options for Pins A and C.

| Inp                                   | uts | Y Output (Channel 1) Logic Options |      |        |       |       |        |        |         |               |                  |

|---------------------------------------|-----|------------------------------------|------|--------|-------|-------|--------|--------|---------|---------------|------------------|

| A                                     | В   | A•B                                | A•/B | /A • B | /A•/B | A + B | A + /B | /A + B | /A + /B | Buffer<br>Y=A | Inverter<br>Y=/A |

| 0                                     | 0   | 0                                  | 0    | 0      | 1     | 0     | 1      | 1      | 1       | 0             | 1                |

| 0                                     | 1   | 0                                  | 0    | 1      | 0     | 1     | 0      | 1      | 1       | 0             | 1                |

| 1                                     | 0   | 0                                  | 1    | 0      | 0     | 1     | 1      | 0      | 1       | 1             | 0                |

| 1                                     | 1   | 1                                  | 0    | 0      | 0     | 1     | 1      | 1      | 0       | 1             | 0                |

| Inp                                   | uts | Z Output (Channel 2) Logic Options |      |        |       |       |        |        |         |               |                  |

| с                                     | D   | C۰D                                | C•/D | /C+D   | /C•/D | C+D   | C+/D   | /C + D | /C + /D | Buffer<br>Z=C | Inverter<br>Z=/C |

| 0                                     | 0   | 0                                  | 0    | 0      | 1     | 0     | 1      | 1      | 1       | 0             | 1                |

| 0                                     | 1   | 0                                  | 0    | 1      | 0     | 1     | 0      | 1      | 1       | 0             | 1                |

| 1                                     | 0   | 0                                  | 1    | 0      | 0     | 1     | 1      | 0      | 1       | 1             | 0                |

| 1                                     | 1   | 1                                  | 0    | 0      | 0     | 1     | 1      | 1      | 0       | 1             | 0                |

| 0 = Ground; 1 = Open (high impedance) |     |                                    |      |        |       |       |        |        |         |               |                  |

#### TABLE XLV. DL2 Functions.

Defined Logic (DL3): The DL3 consists of a two-level cascaded Logic Gate that is controlled by combining the two outputs into a third Logic Gate that cascades the results of the two logically independent channels. See Table XLIII and Table XLVI.

Logic Gates 1 and 2 Functions:

- 1) Boolean Logic decode (AND/OR/NAND/NOR, Logic Options 1-8), based on specific input level conditions to provide an output, specified as Ground (0) or Open (1).

- 2) Buffer output provides a filtered state of the input level.

- 3) Not (Inverter) output is orthogonal to the input level.

Logic Gate 3 (Output Y) is normally Ground (0) until a single set of conditions exists on the outputs of Logic Gate 1 (Output T) and Gate 2 (Output S), as determined by the selected configuration from Table XLVI. Output Z is orthogonal to Output Y.

Defined Logic (DL3) input options include specifying Pins A and C as Pull-up or Pull-down at the time of part configuration. See Input Level Options for Pins A and C.

| TABLE XLVI. | DL3 Functions. |

|-------------|----------------|

|             |                |

| in a                                  |    | Y , Z Output (Gate 3) Logic Options |        |        |         |  |  |  |  |

|---------------------------------------|----|-------------------------------------|--------|--------|---------|--|--|--|--|

| Inpo                                  | 15 | T+S                                 | T • /S | /T • S | /T • /S |  |  |  |  |

| т                                     | s  | Y,Z                                 | Y,Z    | Y,Z    | Y,Z     |  |  |  |  |

| 0                                     | 0  | 0,1                                 | 0,1    | 0,1    | 1,0     |  |  |  |  |

| 0                                     | 1  | 0,1                                 | 0,1    | 1,0    | 0,1     |  |  |  |  |

| 1                                     | 0  | 0,1                                 | 1,0    | 0,1    | 0,1     |  |  |  |  |

| 1                                     | 1  | 1,0                                 | 0,1    | 0,1    | 0,1     |  |  |  |  |

| ) = Ground: 1 = Open (high impedance) |    |                                     |        |        |         |  |  |  |  |

|          |             |            |                                 |        |        |           |            |        |         |               |                  | · • • • • • • • • |

|----------|-------------|------------|---------------------------------|--------|--------|-----------|------------|--------|---------|---------------|------------------|-------------------|

| Inp      | puts        |            |                                 |        | T Outp | out (Gate | 1) Logic O | ptions |         |               |                  |                   |

| A        | в           | A٠B        | A•/8                            | /A • B | /A•/B  | A+B       | A + /B     | /A + B | /A + /B | Buffer<br>T=A | Inverter<br>T=/A | T T               |

| 0        | 0           | 0          | 0                               | 0      | 1      | 0         | 1          | 1      | 1       | 0             | 1                | ו ור              |

| 0        | 1           | 0          | 0                               | 1      | 0      | 1         | 0          | 1      | 1       | 0             | 1                | I DI              |

| 1        | 0           | 0          | 1                               | 0      | 0      | 1         | 1          | 0      | 1       | 1             | 0                |                   |

| 1        | 1           | 1          | 0                               | 0      | 0      | 1         | 1          | 1      | 0       | 1             | 0                | ן ע               |

| Ing      | outs        |            | S Output (Gate 2) Logic Options |        |        |           |            |        |         |               |                  |                   |

| c        | D           | C۰D        | C•/D                            | /C • D | /C+/D  | C+D       | C+/D       | /C + D | /C + /D | Buffer<br>S=C | Inverter<br>S=/C |                   |

| 0        | 0           | 0          | 0                               | 0      | 1      | 0         | 1          | 1      | 1       | 0             | 1                | ו רו              |

| 0        | 1           | 0          | 0                               | 1      | 0      | 1         | 0          | 1      | 1       | 0             | 1                |                   |

| 1        | 0           | 0          | 1                               | 0      | 0      | 1         | 1          | 0      | 1       | 1             | 0                |                   |

| 1        | 1           | 1          | 0                               | 0      | 0      | 1         | 1          | 1      | 0       | 1             | 0                | J                 |

| 0 = Grou | ind; 1 = Op | en (high i | mpedance                        | 2)     |        |           |            |        |         |               |                  |                   |

Defined Logic (DL4): monitors and decode up to 4 discrete inputs and provides two orthogonal outputs. See Table XLIII. DL4 can also function as a 4-bit binary or binary-coded decimal (BCD) decoder.

The Output Y is normally Ground (0) until a single set of conditions exists on the four (A - D) discrete inputs.

When that single set of conditions occurs, Output Y will go Open (1). See Table XLVII. Output Z is orthogonal to Output Y. Output Z will remain Open (1) until the same set of conditions specified above occurs, at which time it will become Ground (0). See Table XLVII.

Defined Logic (DL4) input options include specifying Pins A and C as Pull-up or Pull-down at the time of part configuration. See Input Level Options for Pins A and C.

## TABLE XLVII. <u>DL4 Functions</u>.

|       |       |         |        |            |       |      |       |       |       |       | Logic ( | options |       |       |       |        |        |         |        |

|-------|-------|---------|--------|------------|-------|------|-------|-------|-------|-------|---------|---------|-------|-------|-------|--------|--------|---------|--------|

|       | Inp   | wts     |        | A-B-       | A-B-  | A-B- | A-B-  | A+/B+ | A+/B+ | A-/B- | A-/8-   | /A+B+   | /A-B- | /A-B- | /A-B- | /A+/B+ | /A+/B+ | /A•/B/• | /A-/B- |

|       |       |         |        | C-D        | C+/D  | /C•D | /C+/D | C-D   | C•/D  | /C+D  | /C•/D   | C-D     | C•/D  | /C+D  | /C+/D | C-D    | C+/D   | /C-D    | /C+/D  |

|       |       |         | _      |            |       |      |       |       |       |       | Out     | puts    |       |       |       |        |        |         |        |

| Α     | В     | c       | D      | Y,Z        | Y,Z   | Y,Z  | Y,Z   | Y,Z   | Y,Z   | Y,Z   | Y,Z     | Y,Z     | Y,Z   | Y,Z   | Y,Z   | Y,Z    | Y,Z    | Y,Z     | Y,Z    |

| 0     | 0     | 0       | 0      | 0,1        | 0,1   | 0,1  | 0,1   | 0,1   | 0,1   | 0,1   | 0,1     | 0,1     | 0,1   | 0,1   | 0,1   | 0,1    | 0,1    | 0,1     | 1,0    |

| 0     | 0     | 0       | 1      | 0,1        | 0,1   | 0,1  | 0,1   | 0,1   | 0,1   | 0,1   | 0,1     | 0,1     | 0,1   | 0,1   | 0,1   | 0,1    | 0,1    | 1,0     | 0,1    |

| 0     | 0     | 1       | 0      | 0,1        | 0,1   | 0,1  | 0,1   | 0,1   | 0,1   | 0,1   | 0,1     | 0,1     | 0,1   | 0,1   | 0,1   | 0,1    | 1,0    | 0,1     | 0,1    |

| 0     | 0     | 1       | 1      | 0,1        | 0,1   | 0,1  | 0,1   | 0,1   | 0,1   | 0,1   | 0,1     | 0,1     | 0,1   | 0,1   | 0,1   | 1,0    | 0,1    | 0,1     | 0,1    |

| 0     | 1     | 0       | 0      | 0,1        | 0,1   | 0,1  | 0,1   | 0,1   | 0,1   | 0,1   | 0,1     | 0,1     | 0,1   | 0,1   | 1,0   | 0,1    | 0,1    | 0,1     | 0,1    |

| 0     | 1     | 0       | 1      | 0,1        | 0,1   | 0,1  | 0,1   | 0,1   | 0,1   | 0,1   | 0,1     | 0,1     | 0,1   | 1,0   | 0,1   | 0,1    | 0,1    | 0,1     | 0,1    |

| 0     | 1     | 1       | 0      | 0,1        | 0,1   | 0,1  | 0,1   | 0,1   | 0,1   | 0,1   | 0,1     | 0,1     | 1,0   | 0,1   | 0,1   | 0,1    | 0,1    | 0,1     | 0,1    |

| 0     | 1     | 1       | 1      | 0,1        | 0,1   | 0,1  | 0,1   | 0,1   | 0,1   | 0,1   | 0,1     | 1,0     | 0,1   | 0,1   | 0,1   | 0,1    | 0,1    | 0,1     | 0,1    |

| 1     | 0     | 0       | 0      | 0,1        | 0,1   | 0,1  | 0,1   | 0,1   | 0,1   | 0,1   | 1,0     | 0,1     | 0,1   | 0,1   | 0,1   | 0,1    | 0,1    | 0,1     | 0,1    |

| 1     | 0     | 0       | 1      | 0,1        | 0,1   | 0,1  | 0,1   | 0,1   | 0,1   | 1,0   | 0,1     | 0,1     | 0,1   | 0,1   | 0,1   | 0,1    | 0,1    | 0,1     | 0,1    |

| 1     | 0     | 1       | 0      | 0,1        | 0,1   | 0,1  | 0,1   | 0,1   | 1,0   | 0,1   | 0,1     | 0,1     | 0,1   | 0,1   | 0,1   | 0,1    | 0,1    | 0,1     | 0,1    |

| 1     | 0     | 1       | 1      | 0,1        | 0,1   | 0,1  | 0,1   | 1,0   | 0,1   | 0,1   | 0,1     | 0,1     | 0,1   | 0,1   | 0,1   | 0,1    | 0,1    | 0,1     | 0,1    |

| 1     | 1     | 0       | 0      | 0,1        | 0,1   | 0,1  | 1,0   | 0,1   | 0,1   | 0,1   | 0,1     | 0,1     | 0,1   | 0,1   | 0,1   | 0,1    | 0,1    | 0,1     | 0,1    |

| 1     | 1     | 0       | 1      | 0,1        | 0,1   | 1,0  | 0,1   | 0,1   | 0,1   | 0,1   | 0,1     | 0,1     | 0,1   | 0,1   | 0,1   | 0,1    | 0,1    | 0,1     | 0,1    |

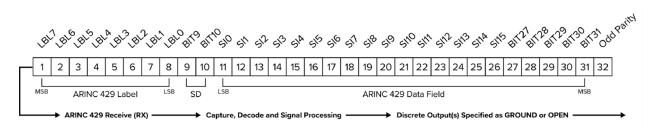

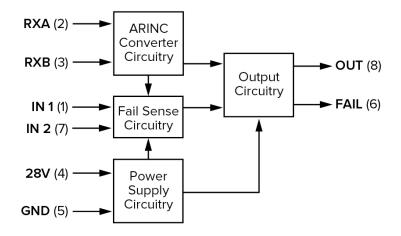

| 1     | 1     | 1       | 0      | 0,1        | 1,0   | 0,1  | 0,1   | 0,1   | 0,1   | 0,1   | 0,1     | 0,1     | 0,1   | 0,1   | 0,1   | 0,1    | 0,1    | 0,1     | 0,1    |